シリコンダイ(die)は、半導体製造の重要な工程で、ウェハー上に回路を焼き付け、切り分けて作られるチップのことです。

本記事では、シリコンダイの概要からその製造工程、技術的な背景まで詳しく説明します。

半導体技術が急速に進歩している中で、シリコンダイの役割を理解することは重要です。

シリコンダイの概要

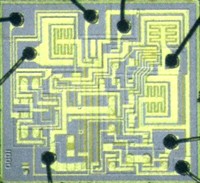

シリコンダイとは、半導体チップの製造工程で用いられる小型のチップで、ウェハーと呼ばれる薄いシリコンの円盤に回路を焼き付け、それを格子状に切り分けることで得られます。

ダイはICチップとしての基礎を形成し、これに金属端子やパッケージが加わることで最終的な半導体製品が完成します。

シリコンウェハーと回路の焼き付け

半導体の製造は、まず直径数十cmのシリコンウェハーを用意し、その表面に配線や素子の回路パターンを焼き付けるところから始まります。

このパターンは碁盤目状に同一のチップが数十枚配置されており、これを切り分けることで個々のダイが形成されます。

ダイとダイサイズ

ダイサイズは、ICチップの面積を示し、一般的には数mmから数cm角です。

このダイサイズが小さいほど、1枚のウェハーから製造できるチップの数が増加し、コスト効率が向上します。

例えば、同じ回路設計を持つチップでも微細化技術を用いることで、より小さなダイサイズで製造することが可能となります。

このプロセスを「シュリンク」と呼びます。

ダイサイズの微細化とコスト削減の関係

半導体製造技術は年々進化し、ウェハー上の回路を微細化する技術も進歩しています。

この進歩により、ダイサイズを縮小しても同じ機能を維持することができ、より高性能なチップを低コストで製造することが可能です。

- シュリンクのメリット:

設計を変更せずに製造プロセスを改善することで、同じウェハーからより多くのダイを得ることができます。

これにより、製造コストが削減され、市場競争力が向上します。

- 技術の進化とダイサイズの縮小:

ナノスケールのプロセス技術を活用することで、より高い集積度と性能を持つチップが作成されます。

例えば、5nmや3nmプロセスといった最新の技術は、従来のプロセスに比べて大幅な微細化を実現しています。

具体的な応用例

シリコンダイは、スマートフォンやパソコンなど、あらゆる電子機器の中核を担っています。

小さなダイサイズのチップは、モバイル機器において特に有利で、消費電力の低減や発熱の抑制が可能です。

また、自動運転技術やAI処理向けの高性能チップでも、微細化技術が活かされています。

まとめ

シリコンダイは、半導体製造の核心的な要素であり、技術の進化に伴い重要性が増しています。

ダイサイズの微細化により、製造効率の向上とコスト削減が図られ、現代のIT産業を支える重要な技術となっています。

半導体の未来を見据える上で、シリコンダイの役割を理解することは不可欠です。

この記事では、シリコンダイに関する基本的な知識と技術的な背景について解説しました。

これを通じて、半導体チップの製造工程やその重要性についての理解が深まることでしょう。