パリティビット(parity bit)は、データ通信やストレージなどの分野で誤りを効率的に検出するために使われる基本的な技術です。

非常にシンプルながら、コンピュータシステムの信頼性を支える重要な役割を果たします。

この記事では、パリティビットの定義・仕組み・種類・限界・実際の利用例について、IT技術者にも納得いただけるように詳しく解説します。

パリティビットとは何か?

基本概念と目的

パリティビットとは、ビット列中の「1」の個数が奇数か偶数かを判断し、その情報を1ビットにまとめて付加する誤り検出符号(エラーチェックコード)の一種です。

-

送信側/記録側:データをビット列に変換し、パリティビットを算出して末尾に付加

-

受信側/読み込み側:同様の計算を行い、付加されたパリティビットと比較

両者が一致しなければデータにエラーが含まれていると判断されます。

パリティビットの種類と判定方法

偶数パリティと奇数パリティの違い

偶数パリティ(Even Parity)

-

パリティビットを付加した全体の「1」の個数が偶数になるように調整

-

例:

1011→ 「1」が3個 → パリティビット =1(合計4個で偶数)

奇数パリティ(Odd Parity)

-

パリティビットを含めて「1」の個数が奇数になるように設定

-

例:

1001→ 「1」が2個 → パリティビット =1(合計3個で奇数)

パリティチェックとの関係

パリティビットは単体では機能しません。

パリティチェックという検証プロセスによってその役割を果たします。

-

検証方法:受け取ったビット列に含まれる「1」の個数を再計算し、パリティビットと照合

-

一致すれば正常または偶数個のビット反転

-

不一致なら奇数個のエラー発生

実際の使用例と注意点

パリティビットの活用シーン

通信プロトコルにおける使用

-

RS-232Cやモデムなどの古典的な通信方式で利用

-

軽量プロトコルでの簡易エラーチェックに最適

メモリと記憶装置での活用

-

パリティ付きメモリ(Parity RAM)でのエラー検出

-

RAIDシステムにおけるパリティコードの使用(RAID5など)

組込み機器・マイコン系の活用例

-

センサーデータの伝送

-

省電力通信デバイスでのビット誤り検出

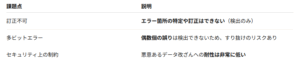

パリティビットの限界とリスク

そのため、信頼性が重視される領域では、CRC(巡回冗長検査)やECC(エラー訂正符号)との併用が推奨されます。

実用上の補足:バースト誤りとの関係

バーストエラーとは、連続する複数ビットの誤りです。これは単一のパリティビットでは検出が難しく、パリティビットだけでの対応は非現実的です。

そのため、バースト誤りに対しては以下のような対策が必要です:

-

垂直・水平パリティの併用(2次元パリティチェック)

-

Hamming符号やBCHコードなどの訂正可能な方式への移行

まとめ

パリティビットは、コンピュータや通信分野におけるもっとも基本的な誤り検出技術の一つです。

特に以下の点が重要です:

-

シンプルかつ高速に誤りを検出可能

-

偶数パリティと奇数パリティの2種類が存在

-

エラーの訂正は不可、あくまで検出に特化

-

実際には通信やメモリ保護、RAID構成などで活用

-

高信頼が求められる環境では高度な誤り検出技術と併用が必要

パリティビットは単純ながら、エラー検出の第一歩として非常に重要です。

適切な使用と、限界を補う設計が求められます。