現代のコンピュータのほとんどが採用しているノイマン型コンピュータ(von Neumann architecture)。

このアーキテクチャは、プログラムとデータを共通の記憶装置に格納し、順次実行する方式であり、「ストアードプログラム方式」としても知られています。

この記事では、ノイマン型コンピュータの基本原理、構成要素、利点と欠点、さらには現代における技術的な課題までを、IT専門の視点でわかりやすく解説します。

ノイマン型コンピュータとは何か?

ストアードプログラム方式の基本概念

ノイマン型コンピュータとは、プログラム(命令)とデータを同一の主記憶装置に格納し、順次CPUがそれを読み込んで実行する構造のことを指します。

1945年にジョン・フォン・ノイマンらによって提唱されたこのモデルは、ソフトウェアという概念の出発点にもなりました。

特徴:

-

プログラムを書き換えることで処理内容を柔軟に変更可能

-

汎用性が高く、再配線が不要

-

現代のほぼすべてのCPUアーキテクチャに継承されている

歴史的背景とEDVACの開発

ノイマン型アーキテクチャの発端は、第二次世界大戦後に開発されたEDVACという電子計算機プロジェクトです。当初のコンピュータ(例:ENIAC)は、配線を物理的に変更しないと別の計算ができない仕様でした。

これに対し、ノイマンらが提唱した「プログラム内蔵方式」は、記憶装置に格納された命令をソフトウェアとして扱うことで、プログラムの柔軟性と拡張性を飛躍的に高めました。

ノイマン型コンピュータの構成要素

主な5つの要素

-

演算装置(Arithmetic Logic Unit, ALU)

四則演算や論理演算などを担当します。 -

制御装置(Control Unit)

命令の解釈と実行の制御を行います。 -

記憶装置(Main Memory)

プログラムとデータの両方を格納します。 -

入力装置(Input)

キーボードやセンサーなど、データをコンピュータに取り込む手段。 -

出力装置(Output)

モニターやプリンターなど、結果を外部に出力します。

これらは現代のコンピュータシステムでも基本的に踏襲されており、マイクロプロセッサ内部の回路設計にも影響を与えています。

フォンノイマンボトルネックとは?

性能の律速要因

ノイマン型コンピュータの構造的な弱点として知られるのが、フォンノイマンボトルネック(von Neumann bottleneck)です。

これは、CPUと主記憶間のバス(伝送路)が1本で共有されていることによって、命令とデータの読み書きが競合し、処理速度が制限されてしまう現象です。

実際の影響例:

-

CPUクロックが高速でも、メモリの読み書き速度が追いつかず待機時間が発生

-

プログラム実行中のパフォーマンス低下

対応策:キャッシュメモリの活用

現代のプロセッサでは、この問題を緩和するために多層キャッシュ(L1/L2/L3)が導入されています。

キャッシュ階層の概要:

-

L1キャッシュ:CPUに最も近く、高速だが容量は小さい(数十KB程度)

-

L2キャッシュ:L1よりやや遅いが容量が大きい(数百KB〜数MB)

-

L3キャッシュ:複数コアで共有する大容量キャッシュ(数MB〜数十MB)

この階層構造により、頻繁に使用されるデータや命令をCPU近くに保持し、主記憶へのアクセス回数を最小限に抑える工夫がなされています。

ノイマン型以外のアーキテクチャと比較

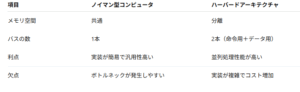

ハーバードアーキテクチャとの違い

ハーバードアーキテクチャは、命令とデータを別々のメモリ空間に保持する構造です。

これは組み込みシステムやDSP(デジタル信号処理)などで多く採用されています。

現代ITにおけるノイマン型の重要性と限界

ノイマン型アーキテクチャは、70年以上にわたり進化を続けながら現代のOS、アプリケーション、プロセッサ設計の基盤となっています。

しかし、AIやビッグデータ、量子コンピューティングのような次世代技術では、非ノイマン型アーキテクチャの導入も模索されています。

今後の方向性:

-

ニューラルネットワーク処理向けのノイマン非依存構造

-

並列分散処理との併用による新しいハイブリッドモデル

まとめ

ノイマン型コンピュータは、今日のコンピュータシステムにおける基本的な設計様式として広く採用されており、プログラム内蔵方式(ストアードプログラム方式)という画期的な発想によって、汎用性と効率性を実現してきました。

一方で、フォンノイマンボトルネックという性能面での課題もあり、現代ではキャッシュ技術や新しいアーキテクチャとの併用によってこれを克服しています。

今後も、ノイマン型の設計思想は継承されつつも、用途や目的に応じたアーキテクチャの最適化が進むことでしょう。

IT技術者や開発者にとって、この基礎を理解することは不可欠です。